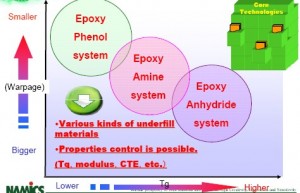

前日在学习Underfill Roadmap—By Namics资料时碰到一个Low-K的概念,不甚了解,后来在网上查实了一下,就转了这篇文章过来了:

Low-K技术最初由IBM开发,当时的产业大背景是——随着电路板蚀刻精度越来越高,芯片上集成的电路越来越多,信号干扰也就越来越强,所以IBM致力于开发、发展一种新的多晶硅材料。IBM声称,Low-K材料帮助解决了芯片中的信号干扰问题。而Intel的目的是使用低介电常数的材料来制作处理器导线间的绝缘体。这种材料可以很好地降低线路间的串扰,从而降低处理器的功耗,提高处理器的高频稳定性。在Intel的产品开发中Northwood应该就已经受福于Low-K技术了。不过,现在的Low-K技术已经不是Northwood时代的Low-K技术了,记得我以前在一个帖子就曾经强调过,硬件发展在三大技术——晶圆切割技术、电路板蚀刻技术和晶体管的纳米级别的集成技术,这三大技术的快速发展而带来空前活力的同时,我们应该可以预见到越来越高的频率、越来越大的功耗和越来越夸张的发热。所以,我觉得Low-K技术将人们的关注重点再一次转移到了材料科学上,而这才是真正针对处理器高频率低稳定高热量这个当前最大难题的治本的办法,尽管事实上,当前的Low-K技术还不足以解决这些问题。

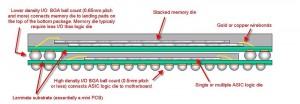

随着Prescott的出现,它采用的7层Low-K绝缘层的铜连接和最新的低介电CDO绝缘体,这连个亮点,在Intel的技术白皮书中已经被称作,最大的减少了铜互连的导线之间的电容,有效提高了芯片中的信号速度和减少Prescott的功耗。

另外,在过去30年多来,业界的绝缘材料技术主要集中在SiO2上,SiO2里面的新材料每个月都在变,但就是SiO2自己不变。这里需要说明一点是,这个材料也是IBM开发的。SiO2的相对介电常数相对当时是很理想的,虽然还不是完美,大约在4-5之间。如果翻一下电子的参考资料,即使像等离子CVD方法制造的SiO2材料,相对介电仍然高达3.8。相比之下Low-K介电常数一般在2.5左右。在抑制漏电流干扰方面,理论上是完美的。电子教材上,对于低介电材料的描述很简短,类似于“……可以很好减少电信号传播时由于电路本身的阻抗和容抗延迟所带来的信号衰减”等等。

然后说说Low-K的缺点。我认为Low-K目前最大缺点是实际应用效果不明显,需要新的材料的介入,比如从有机材料领域寻求发展(曰、美科学家目前已经做到这点了)。Low-K材料的开发速度可以说是空前迅猛的,前景光明。不过还是需要注意一些老问题,比如工艺不成熟、铜互连技术缺陷还有良品率(良品率低下的都是开使用新材料、新工艺先河的公司比如Intel比如nVidia)问题等等。

说了那么多Low-K,现在说说High-K技术。

Intel宣布已经完成了对High-K金属门电路晶体管技术的研发,这个消息比较新,看到以后,我去网上找了找,,该技术的应用不像Low-K,短时期是无法投入实际应用的(主要是技术原因),不过我还是觉得有必要来解释一下这个技术,主要是与Low-K的区别,不要混淆。

首先,我们知道,目前使用最最广泛的晶体管是CMOS晶体管,CMOS晶体管特点是什么?首先CMOS晶体管功耗和抗干扰能力优于同时期的TTL器件,而且速度和TTL器件相当,所以CMOS取代TTL是大势所趋,我们看到目前集成电路上的晶体管还有几乎所有PLD器件都是采用CMOS技术,这一点就说明了CMOS的大行其道。不过,在High-K材料应用之后,情况可能将会有所改变。

转载地址:http://hi.baidu.com/cmf3887299/blog/item/5811fdfdc2592d47d7887d58.html

已有 2 个评论

联系站长

Email:Anndiqiu#Gmail.com

Mobile Phone:13923499497

热门文章

数字

$2,242.7 Million Explore Global laminating adhesives market that is poised to be worth $2,242.7 million by 2019 了解更多 »