前言及序言(点击链接查看之)——————————–1

第1章 半导体工业————————————–2—3

第2章 半导体材料和工艺化学品————————–4—5

第3章 晶圆制备——————————————-6

第4章 芯片制造概述————————————7—8

第5章 污染控制—————————————9—10

第6章 工艺良品率————————————11—12

第7章 氧化——————————————13—14

第8章 基本光刻工艺流程—从表面准备到曝光————15—17

第9章 基本光刻工艺流程—从曝光到最终检验————18—20

第10章 高级光刻工艺———————————21—23

第11章 掺杂—————————————–24—26

第12章 淀积—————————————–27—29

第13章 金属淀积————————————-30—31

第14章 工艺和器件评估——————————-32—33

第15章 晶圆加工中的商务因素————————-34—35

第16章 半导体器件和集成电路的形成———————–36

第17章 集成电路的类型——————————-37—38

第18章 封装—————————————–39—41

个人感慨—————————————————41

全文 »

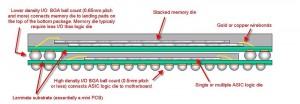

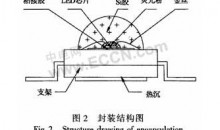

1、影响封装工艺的芯片特性:

a.集成度、晶片厚度、尺寸、对环境的敏感度、物理的脆弱度、热的产生、热敏感度;

b.影响封装工艺的环境和物理因素可以从两个方面来阐述,第一是临近晶片制造工艺结尾处的钝化层淀积(主要是氧化硅和氮化硅及掺杂一些硼、磷或两者兼备),第二种保护芯片的方法就是提供一个封装体;

c.封装设计要考虑散热的因素,热同样也是封装工艺中的一项重要参数,封装工艺的耐热极限是450度;

2、封装功能和设计:

a.紧固的引脚系统

b.物理性保护

c.环境性保护

d.散热

3、封装操作工艺概述:

a.洁净度和静电控制

■HEPA过滤器/VLF空气、面罩帽子和鞋套、指套或手套、过滤的化学品、粘着地垫

■接地的静电腕带、静电服、防静电材料、设备接地、工作平台接地、地板接地

b.基本工艺流程

底部准备、划片、取片和承载、检查、粘片、打线、封装前检查、封装、电镀、切筋成型、印字、最终测试

c.常用的封装件

■芯片的粘贴区域

■内部和外部的引脚

■芯片-封装体的连接

■封装(密封性、非密封性/弱密封性) 全文 »

1、大多数电路按其特定的设计原理和功能可以分成三种基本类型:逻辑电路、存储电路和微处理器(逻辑与存储),电路的多样性主要来自于大量特殊用途参数的转变;

2、电路基础:在电路中,数字由二进制码来编码、存储和操作,这都是因为电容可以通过充电得到一个电荷或没有电荷,晶体管也可以开或关,电路中记录信息的最小单位称为“二进制数”或“位”,8位称为一个字节;

3、集成电路的类型:

a.逻辑电路:

■模拟-数字逻辑电路

■模拟逻辑电路

RTL 电阻器-晶体管逻辑

DTL 二极管-晶体管逻辑

TTL 晶体管-晶体管逻辑

ECL 发射极-耦合电路

DCTL 直接-耦合晶体管逻辑

I2L 集成注入晶体管逻辑

■定制-半定制逻辑

全定制

标准电路-定制门形式

标准电路-选择连线门阵列

可编程的阵列逻辑(PAL) 全文 »

1、半导体器件的生成:电阻器、电容器、二极管、晶体管、熔断器、导体;

2、电阻器:掺杂型电阻器、EPI电阻器、Pinch电阻器、薄膜电阻器;

3、电容器:氧化硅电容器、结电容器、沟槽电容器、堆叠电容器(stacked capacitor);

4、二极管:掺杂二极管(击穿电压breakdown)、Schottky barrier二极管(欧姆接触);

5、晶体管:双极型晶体管(transfer resistor)、Schottky barrier双极型晶体管;

6、场效应晶体管(FET):金属栅型MOS场效应晶体管、硅栅极型MOS、多晶硅栅型MOS、硅化物栅极型MOS、V凹槽型MOS(VMOS)、扩散型MOS(DMOS)、存储器MOS(MMOS)、结型场效应晶体管(JFET)、金属半导体场效应晶体管(MESFET);

7、熔断器和导体:(underpass conductor 地下导体); 全文 »

1、制造和工厂经济:

尽管有在工艺、成本以及市场方面的诸多变化,衡量芯片制造领域的财政状况的方法依然相同:即对于芯片厂售出的有功能的芯片,每片的成本如何(the cost per functioning die shipped out of fabrication)等;在因拥有了封装能力而完全扩展为商业工厂后,衡量方式又变成每一片售出的芯片成本(the cost per die shipped);在百万级的集成电路世界,每个晶体管的成本正成为一个指示参数。

2、晶圆的制造成本:

a.固定成本:

■管理费用(行政人员数量增长快于生产人员;工厂设施成本及设施维护费用等)

■设备(折旧)

b.非固定成本

■材料:直接材料(进入到芯片中或加在芯片上的材料)和非直接材料(掩膜版等化学品)

■劳动力:直接劳动力和非直接劳动力

■良品率:有良品率的芯片成本(yielded die cost)和未有良品率的芯片成本(unyield die cost)

3、生产成本因素:

a.300毫米直径的晶圆成本估算: 折旧35% 劳动力7% 维护7% 消耗品(直接材料12% 测试晶圆6% 非直接材料26%) 其他7%

b.账面-单据(book to bill)比率

c.生产策略

d.污染控制系统 全文 »

1、从工艺控制和改进的观点来看,关于测量的收集分为三大类:一是包括对测试晶圆和实际器件电性的测量;二是直接测量某些物理参数例如层的厚度、宽度、组成等等;三是测量晶圆和材料内部的污染;

2、晶圆的电性测量:

a.电阻和电阻率及其测量:四探针测试仪(还可测试方块电阻及导电层厚度)

b.掺杂浓度、深度图解法(扩散电阻、阳极氧化技术)

c.二次离子质谱法(SIMS)

d.差动霍尔效应(DHE)

e.氧化层击穿(BVox或击穿电压、GOI)

f.物理测试方法(FIB)

3、晶圆层厚的测量:

a.颜色(由透明镀膜材料的反射系数、观察角度和镀膜的厚度决定)

b.条纹法

c.分光光度计/反射系数

d.椭偏仪

e.触针

4、晶圆的结深:

a.凹槽和斑点(刻蚀技术和点解斑点)

b.扫描电镜(SEM)厚度测量

c.扩散电阻测试法(SRP)

d.二次离子质谱法(SIM)

e.扫描电容显微镜(SCM)及原子力显微镜(AFM) 全文 »

1、虽然掺杂的区域和PN结形成电路中的有源元件,但是需要各种其它的半导体、绝缘介质和导电层完成器件/电路的电器性能,其中的一些是通过化学气相淀积CVD和物理气相淀积PVD的方式淀积在晶圆的表面;常规的淀积层有:掺杂的硅层(外延层)、金属间的绝缘介质层(IMD)、金属间的导电连线、金属导体层和最后的钝化层;半导体薄膜的参数:

■厚度/均匀性;(高纵横比模式)

■表面平整度/粗糙度;

■组成/核粒(grain)尺寸;

■自由应力;

■纯净度;

■完整性;

■电容;(金属传导层-高传导、低电阻低电容的低k介质;绝缘介质-高电容或高k值介质)

关于low-k值和high-k值可参看另一篇日志:什么是Low-K?什么是High-K?

2、化学气相淀积CVD基础:

a.淀积(deposition)指一种材料以物理的方式沉积在晶圆表面上的工艺过程,而生长膜是从晶圆表面的材料上生长形成的; 全文 »

1、结的定义:结(junction)就是富含电子区域(N型区)与富含空穴区域(P型区)的分界处,具体位置就是电子浓度和空穴浓度相同的地方,靠热扩散或离子注入可形成结;

2、掺杂区和结的扩散形成:

a.扩散:是一种材料通过另一种材料的运动,是一种自然的化学过程。两个必要条件一是一种材料的浓度必须高于另外一种材料的浓度,其次是系统内部必须有足够的能量使高浓度的材料进入或通过另一种材料;

b.NP结:掺杂区中N型原子的浓度较高,反之PN结掺杂区中P型原子的浓度较高;

c.扩散工艺的目的:

■在晶圆表面产生具体掺杂原子的数量(浓度);

■在晶圆表面下的特定位置处形成NP(或)PN结;

■在晶圆表面层形成特定的掺杂原子(浓度)分布。

d.横向(lateral)或侧向(side)扩散、同型掺杂(不会形成结);

e.结的图形显示、浓度随深度变化的曲线;

3、扩散工艺的步骤:固态扩散工艺(solid-state diffusion)形成结需要两步:淀积(deposition)和推进氧化(drive-in-oxidation),均在水平或垂直的炉管中进行。 全文 »

1、ULSI/VLSI集成电路图形处理过程中存在的问题:

光学曝光设备的物理局限、光刻胶分辨率的限制、许多与晶片表面有关的问题;

使用光学光刻技术解析0.5微米和0.3微米的图形需要对虚像(aerial images)有很好的控制,控制方法主要从三个方面入手:光学系统分辨率、光刻胶分辨率和晶片表面问题,第四个方面是刻蚀图形定义问题;

2、光学系统分辨率控制:(光刻分辨率工艺路线图)

I线→I线+ARI→I线+OAI/深紫外光/深紫外光+OAI或PSM→I线+ OAI或PSM/深紫外光+ARI或OAI→I线+PSM/深紫外光+OAI或PSM→深紫外光+PSM(最小分辨率减小,ARI环形灯光源、OAI偏轴光源、PSM相位偏移掩膜)

a.改进的曝光源:紫外光UV和深紫外光DUV,汞灯(I线365nm H线405nm G线436nm 中紫外线313nm、深紫外线245nm);

b.受激准分子激光器:XeF 351nm XeCl 308nm RF 248nm AF 193nm;

c.聚焦离子束:系统稳定性非常差;

d.X射线:需要特制掩膜版(金做阻挡层)、成本非常高;

e.电子束:电子束光刻是一门成熟的技术,无需掩膜版,直接书写(direct writing),光刻胶曝光顺序分为光栅式和矢量式;成本也比较高 全文 »

1、显影:通过对未聚合光刻胶的化学分解来使图案显影,显影技术被设计成使之把完全一样的掩膜版图案复制到光刻胶上。

a.负光刻胶显影:二甲苯或stoddart溶剂显影,n-丁基醋酸盐冲洗;

b.正光刻胶显影:碱(氢氧化钠或氢氧化钾)+水溶液、或叠氮化四甲基铵氢氧化物的溶液(TMAH);

c.湿法显影:

沉浸-增加附属方法提高显影工艺,机械搅动、超声波或磁声波等;

喷射-对负胶而言是标准工艺,对温度敏感的正胶却不是很有效,隔热冷却(adiabatic cooling);

混凝-是用以获得正胶喷射显影工艺优点的一种工艺变化;

等离子去除浮渣-不完全显影造成的一个特俗困难叫做浮渣(scumming),用氧等离子去除;

d.干法(或等离子)显影:干法光刻胶显影要求光刻胶化学物的曝光或未曝光的部分二者之一易于被氧等离子体去除,换言之图案的部分从晶圆表面上氧化掉,一种DESIRE的干法显影工艺会使用甲基硅烷和氧等离子体

2、硬烘焙:与软烘焙一样通过溶液的蒸发来固化光刻胶,常见工艺流程如下:

显影—检验—硬烘焙—刻蚀;显影/烘焙—检验—刻蚀;显影/烘焙—检验—重新烘焙—刻蚀;

硬烘焙温度的上限是以光刻胶流动点而定,高温烘焙会产生边缘线等不良现象; 全文 »

《【扒一扒】日本高纯球形硅微粉材料生产商》: 作为一种无机非金属矿物功能性粉体材料,硅微粉广泛应用于电子材料、电工绝缘材料、胶黏剂、特种陶瓷、精密铸造、油漆涂料、油墨、硅橡胶等领域。 目前,世界上只有中国、日本、韩国、美国等少数国家具备硅微粉生产能力... 全文 ?